### MTP50P03HDL

Preferred Device

## Power MOSFET 50 Amps, 30 Volts, Logic Level

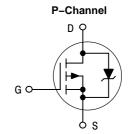

P-Channel TO-220

This Power MOSFET is designed to withstand high energy in the avalanche and commutation modes. The energy efficient design also offers a drain—to—source diode with a fast recovery time. Designed for low voltage, high speed switching applications in power supplies, converters and PWM motor controls, these devices are particularly well suited for bridge circuits where diode speed and commutating safe operating areas are critical and offer additional safety margin against unexpected voltage transients.

#### **Features**

- Avalanche Energy Specified

- Source-to-Drain Diode Recovery Time Comparable to a Discrete Fast Recovery Diode

- Diode is Characterized for Use in Bridge Circuits

- I<sub>DSS</sub> and V<sub>DS(on)</sub> Specified at Elevated Temperature

- Pb-Free Package is Available\*

#### MAXIMUM RATINGS (T<sub>C</sub> = 25°C unless otherwise noted)

| Rating                                                                                                                                                                                                                | Symbol                               | Value           | Unit       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|------------|

| Drain-Source Voltage                                                                                                                                                                                                  | V <sub>DSS</sub>                     | 30              | Vdc        |

| Drain–Gate Voltage ( $R_{GS} = 1.0 \text{ M}\Omega$ )                                                                                                                                                                 | $V_{DGR}$                            | 30              | Vdc        |

| Gate–Source Voltage  – Continuous  – Non–Repetitive (t <sub>p</sub> ≤ 10 ms)                                                                                                                                          | V <sub>GS</sub><br>V <sub>GSM</sub>  | ± 15<br>± 20    | Vdc<br>Vpk |

| Drain Current – Continuous<br>– Continuous @ 100°C<br>– Single Pulse (t <sub>p</sub> ≤ 10 μs)                                                                                                                         | I <sub>D</sub><br>I <sub>D</sub>     | 50<br>31<br>150 | Adc<br>Apk |

| Total Power Dissipation<br>Derate above 25°C                                                                                                                                                                          | P <sub>D</sub>                       | 125<br>1.0      | W<br>W/°C  |

| Operating and Storage Temperature Range                                                                                                                                                                               | T <sub>J</sub> , T <sub>stg</sub>    | -55 to<br>150   | °C         |

| Single Pulse Drain–to–Source Avalanche Energy – Starting $T_J = 25^{\circ}\text{C}$ ( $V_{DD} = 25 \text{ Vdc}, V_{GS} = 5.0 \text{ Vdc}, \text{ Peak}$ $I_L = 50 \text{ Apk}, L = 1.0 \text{ mH}, R_G = 25 \Omega$ ) | E <sub>AS</sub>                      | 1250            | mJ         |

| Thermal Resistance, Junction-to-Case Junction-to-Ambient, when mounted with the minimum recommended pad size                                                                                                          | R <sub>θJC</sub><br>R <sub>θJA</sub> | 1.0<br>62.5     | °C/W       |

| Maximum Lead Temperature for Soldering Purposes, 1/8" from case for 10 seconds                                                                                                                                        | T <sub>L</sub>                       | 260             | °C         |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

ON Semiconductor®

# 50 AMPERES, 30 VOLTS $R_{DS(on)} = 25 \text{ m}\Omega$

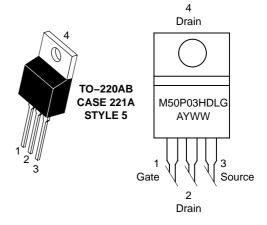

## MARKING DIAGRAM & PIN ASSIGNMENT

M50P03HDL = Device Code A = Assembly Location

Y = Year

WW = Work Week

G = Pb-Free Package

#### ORDERING INFORMATION

| Device       | Package               | Shipping      |

|--------------|-----------------------|---------------|

| MTP50P03HDL  | TO-220AB              | 50 Units/Rail |

| MTP50P03HDLG | TO-220AB<br>(Pb-Free) | 50 Units/Rail |

**Preferred** devices are recommended choices for future use and best overall value.

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### MTP50P03HDL

### **ELECTRICAL CHARACTERISTICS** ( $T_J = 25^{\circ}C$ unless otherwise noted)

| CI                                                                                                                                                                        | naracteristic                                                                                                                   | Symbol               | Min     | Тур          | Max        | Unit         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|--------------|------------|--------------|

| OFF CHARACTERISTICS                                                                                                                                                       |                                                                                                                                 |                      |         |              |            |              |

| Drain-to-Source Breakdown Voltage                                                                                                                                         | (C <sub>pk</sub> ≥ 2.0) (Note 3)                                                                                                | V <sub>(BR)DSS</sub> |         |              |            | Vdc          |

| $(V_{GS} = 0 \text{ Vdc}, I_D = 250 \mu\text{Adc})$<br>Temperature Coefficient (Positive)                                                                                 | · F                                                                                                                             | (=1,72,00            | 30<br>- | -<br>26      | -<br>-     | mV/°C        |

| Zero Gate Voltage Drain Current ( $V_{DS} = 30 \text{ Vdc}$ , $V_{GS} = 0 \text{ Vdc}$ ) ( $V_{DS} = 30 \text{ Vdc}$ , $V_{GS} = 0 \text{ Vdc}$ , $V_{J} = 0 \text{ Vdc}$ | 125°C)                                                                                                                          | I <sub>DSS</sub>     | -<br>-  | -<br>-       | 1.0<br>10  | μAdc         |

| Gate-Body Leakage Current (V <sub>GS</sub> = ±                                                                                                                            | 15 Vdc, V <sub>DS</sub> = 0 Vdc)                                                                                                | I <sub>GSS</sub>     | -       | -            | 100        | nAdc         |

| ON CHARACTERISTICS (Note 1)                                                                                                                                               |                                                                                                                                 |                      |         |              | •          |              |

| Gate Threshold Voltage ( $V_{DS} = V_{GS}$ , $I_{D} = 250 \mu Adc$ ) Threshold Temperature Coefficient                                                                    | $(C_{pk} \geq 3.0) \; (\text{Note 3})$ t (Negative)                                                                             | V <sub>GS(th)</sub>  | 1.0     | 1.5<br>4.0   | 2.0        | Vdc<br>mV/°C |

| Static Drain-to-Source On-Resistance (V <sub>GS</sub> = 5.0 Vdc, I <sub>D</sub> = 25 Adc)                                                                                 | ce (C <sub>pk</sub> ≥ 3.0) (Note 3)                                                                                             | R <sub>DS(on)</sub>  | _       | 0.020        | 0.025      | Ω            |

| Drain-to-Source On-Voltage ( $V_{GS}$ = ( $I_D$ = 50 Adc) ( $I_D$ = 25 Adc, $T_J$ = 125°C)                                                                                | 10 Vdc)                                                                                                                         | V <sub>DS(on)</sub>  | _<br>_  | 0.83         | 1.5<br>1.3 | Vdc          |

| Forward Transconductance<br>(V <sub>DS</sub> = 5.0 Vdc, I <sub>D</sub> = 25 Adc)                                                                                          |                                                                                                                                 | 9FS                  | 15      | 20           | ı          | mhos         |

| DYNAMIC CHARACTERISTICS                                                                                                                                                   |                                                                                                                                 |                      |         |              |            |              |

| Input Capacitance                                                                                                                                                         | 05)/1- 1/ 01/1-                                                                                                                 | C <sub>iss</sub>     | -       | 3500         | 4900       | pF           |

| Output Capacitance                                                                                                                                                        | $(V_{DS} = 25 \text{ Vdc}, V_{GS} = 0 \text{ Vdc}, f = 1.0 \text{ MHz})$                                                        | C <sub>oss</sub>     | ı       | 1550         | 2170       |              |

| Transfer Capacitance                                                                                                                                                      | ,                                                                                                                               | C <sub>rss</sub>     | -       | 550          | 770        |              |

| SWITCHING CHARACTERISTICS (N                                                                                                                                              | ote 2)                                                                                                                          |                      |         |              |            |              |

| Turn-On Delay Time                                                                                                                                                        |                                                                                                                                 | t <sub>d(on)</sub>   | -       | 22           | 30         | ns           |

| Rise Time                                                                                                                                                                 | $(V_{DD} = 15 \text{ Vdc}, I_D = 50 \text{ Adc},$                                                                               | t <sub>r</sub>       | -       | 340          | 466        |              |

| Turn-Off Delay Time                                                                                                                                                       | $V_{GS} = 5.0 \text{ Vdc}, R_G = 2.3 \Omega)$                                                                                   | t <sub>d(off)</sub>  | -       | 90           | 117        |              |

| Fall Time                                                                                                                                                                 |                                                                                                                                 | t <sub>f</sub>       | ı       | 218          | 300        |              |

| Gate Charge                                                                                                                                                               |                                                                                                                                 | Q <sub>T</sub>       | -       | 74           | 100        | nC           |

| (See Figure 8)                                                                                                                                                            | $(V_{DS} = 24 \text{ Vdc}, I_{D} = 50 \text{ Adc},$                                                                             | Q <sub>1</sub>       | _       | 13.6         | -          | _            |

|                                                                                                                                                                           | $V_{GS} = 5.0 \text{ Vdc}$                                                                                                      | $Q_2$                | -       | 44.8         | -          |              |

|                                                                                                                                                                           |                                                                                                                                 | $Q_3$                | -       | 35           | -          |              |

| SOURCE-DRAIN DIODE CHARACT                                                                                                                                                | ERISTICS                                                                                                                        |                      |         |              |            |              |

| Forward On–Voltage                                                                                                                                                        | $(I_S = 50 \text{ Adc}, V_{GS} = 0 \text{ Vdc})$<br>$(I_S = 50 \text{ Adc}, V_{GS} = 0 \text{ Vdc}, T_J = 125^{\circ}\text{C})$ | V <sub>SD</sub>      | _<br>_  | 2.39<br>1.84 | 3.0        | Vdc          |

| Reverse Recovery Time                                                                                                                                                     |                                                                                                                                 | t <sub>rr</sub>      | _       | 106          | _          | ns           |

| (See Figure 15)                                                                                                                                                           | $(I_S = 50 \text{ Adc}, V_{GS} = 0 \text{ Vdc}, \\ dI_S/dt = 100 \text{ A/}\mu\text{s})$                                        | t <sub>a</sub>       | _       | 58           | _          |              |

|                                                                                                                                                                           |                                                                                                                                 | t <sub>b</sub>       | _       | 48           | _          |              |

| Reverse Recovery Stored Charge                                                                                                                                            |                                                                                                                                 | Q <sub>RR</sub>      | _       | 0.246        | -          | μC           |

| INTERNAL PACKAGE INDUCTANCE                                                                                                                                               | <u> </u>                                                                                                                        | 1                    |         |              | I.         |              |

| Internal Drain Inductance<br>(Measured from contact screw on<br>(Measured from the drain lead 0.29)                                                                       |                                                                                                                                 | L <sub>D</sub>       | _<br>_  | 3.5<br>4.5   | _<br>_     | nH           |

| Internal Source Inductance (Measured from the source lead 0.25" from package to source bond pad)                                                                          |                                                                                                                                 | LS                   | _       | 7.5          | _          | nH           |

<sup>1.</sup> Pulse Test: Pulse Width  $\leq$  300  $\mu$ s, Duty Cycle  $\leq$  2%.

2. Switching characteristics are independent of operating junction temperature.

3. Reflects typical values.  $C_{pk} = \left | \frac{\text{Max limit} - \text{Typ}}{3 \text{ x SIGMA}} \right |$

#### MTP50P03HDL

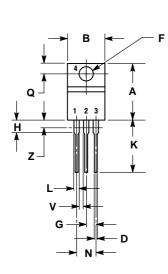

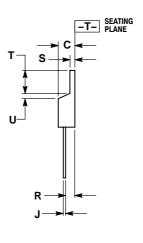

#### **PACKAGE DIMENSIONS**

TO-220 CASE 221A-09 **ISSUE AB**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION Z DEFINES A ZONE WHERE ALL BODY AND LEAD IRREGULARITIES ARE ALLOWED.

|              | INCHES            |            | MILLIMETERS |       |  |

|--------------|-------------------|------------|-------------|-------|--|

| DIM          | MIN               | MAX        | MIN         | MAX   |  |

| Α            | 0.570             | 0.620      | 14.48       | 15.75 |  |

| В            | 0.380             | 0.405      | 9.66        | 10.28 |  |

| C            | 0.160             | 0.190      | 4.07        | 4.82  |  |

| D            | 0.025             | 0.035      | 0.64        | 0.88  |  |

| F            | 0.142             | 0.147      | 3.61        | 3.73  |  |

| G            | 0.095             | 0.105      | 2.42        | 2.66  |  |

| Н            | 0.110             | 0.155      | 2.80        | 3.93  |  |

| J            | 0.018             | 0.025      | 0.46        | 0.64  |  |

| K            | 0.500             | 0.562      | 12.70       | 14.27 |  |

| L            | 0.045             | 0.060      | 1.15        | 1.52  |  |

| N            | 0.190             | 0.210      | 4.83        | 5.33  |  |

| Q            | 0.100             | 0.120      | 2.54        | 3.04  |  |

| R            | 0.080             | 0.110      | 2.04        | 2.79  |  |

| S            | 0.020             | 0.055      | 0.508       | 1.39  |  |

| Т            | 0.235             | 0.255      | 5.97        | 6.47  |  |

| U            | 0.000             | 0.050      | 0.00        | 1.27  |  |

| ٧            | 0.045             |            | 1.15        |       |  |

| Z            |                   | 0.080      |             | 2.04  |  |

| STYLE<br>Pin | 11. GAT<br>2. DRA | IN<br>JRCE |             |       |  |